发布时间:2023-12-23 20:08:48 | 作者: 雷竞技官网官方网站入口

论述伺服驱动控制器的实现方法,通过对ARM+FPGA+DSP架构的多CPU控制器的具体分析将其原理和优势体现出来;这种架构控制器系统分工明确,提高了算法的实时性;提高了控制器对外接口EtherCAT的实时性;提高了系统的稳定性。这种架构方案在天津电气科学研究院有限公司的伺服驱动器产品中进行了实验,现场的应用取得了良好的效果,体现出这种技术的现实意义。

伺服驱动器是用来控制伺服电机的一种控制器,一般是通过位置、速度和力矩三种方式对电机来控制,实现高精度的系统定位。

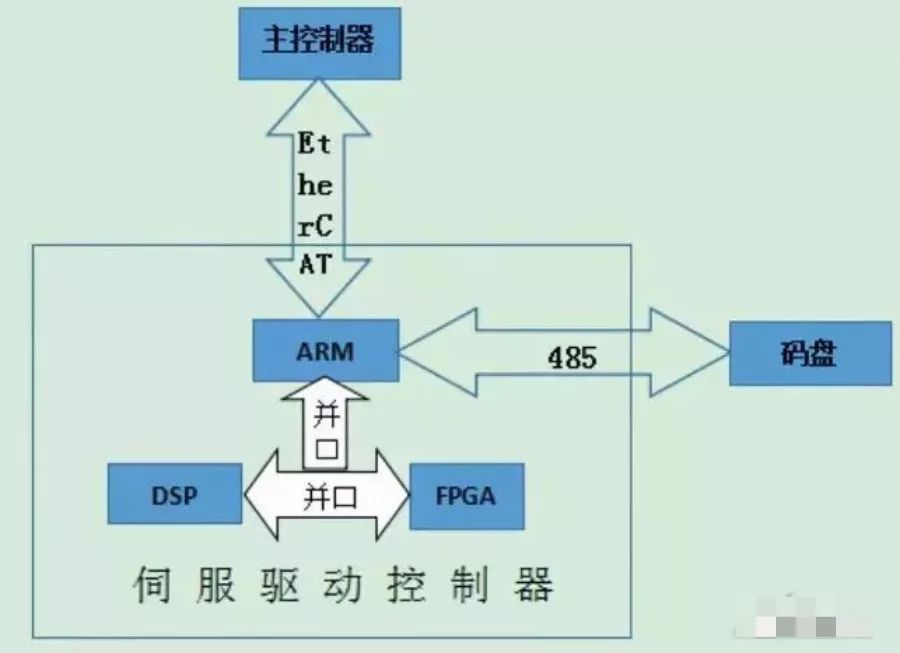

方法3是目前最先进的架构,前两种方法都有局限性。方法1和方法2这种单CPU架构的控制器,一个CPU集算法、采集控制、通讯、显示功能于一体,当算法复杂度和实时性要求高时往往会顾此失彼。而方法3的架构中各个CPU的分工明确,ARM负责通信和显示功能,DSP负责算法运算,FPGA负责采集和控制。方法3的技术瓶颈是满足伺服控制器的实时性要求需要几个CPU之间的高速数据通信,因此,若能够找到一个高速的通信方式可完全发挥各个CPU的特性,就像一个多核CPU在工作一样。

本研究基于ARM+FPGA+DSP架构,采用并口通信的方法用于几个CPU之间的内部高速通信;此外伺服驱动器作为伺服系统的一部分还需要和主控器和编码器进行高速通信,来满足整个伺服系统的实时性要求,本架构采用EtherCAT和高速485接口用于控制器和别的设备进行高速通信,描述了系统的原理架构和软件设计架构。

2.1 此架构的控制器中ARM负责通信和显示功能,DSP负责算法运算,FPGA负责采集和控制,如图1所示。FPGA采集相电压、相电流等物理量通过并口传给DSP;ARM通过EtherCAT接收主控制器命令,通过高速485采集码盘的速度和位置等信息,通过并口传给FPGA中转下再传到DSP;DSP中执行伺服控制的算法,利用FPGA和ARM中采集的数据来进行计算,把计算结果再通过并口传给FPGA和ARM,由FPGA和ARM进行有关的控制操作。

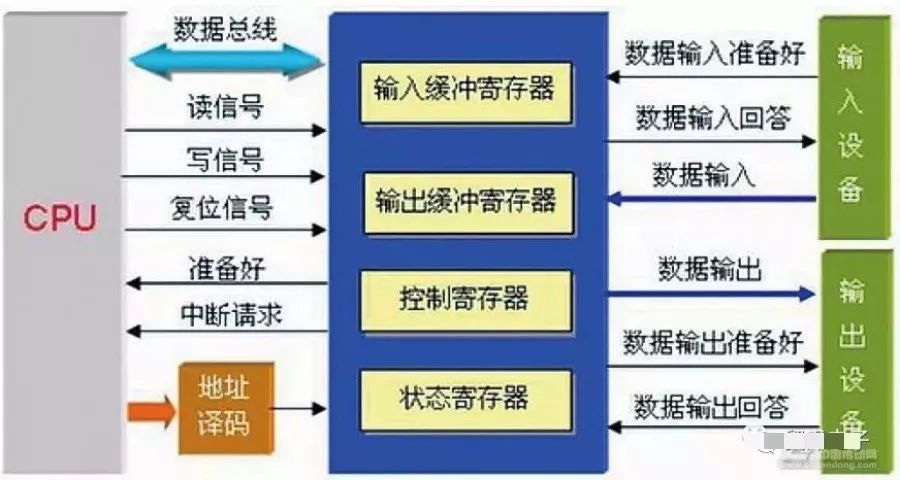

2.2 此架构控制器中几个CPU之间的双口RAM通信:用双口RAM中各位数据都是并行传送的,它通常是以字节(8位)的整数倍为单位做数据传输,能完成数据的输入和输出。用双口RAM通信的原理如2所示。用双口RAM通信具有各数据位同时传输,传输速度快、效率高的特点,多用在实时、快速的场合。

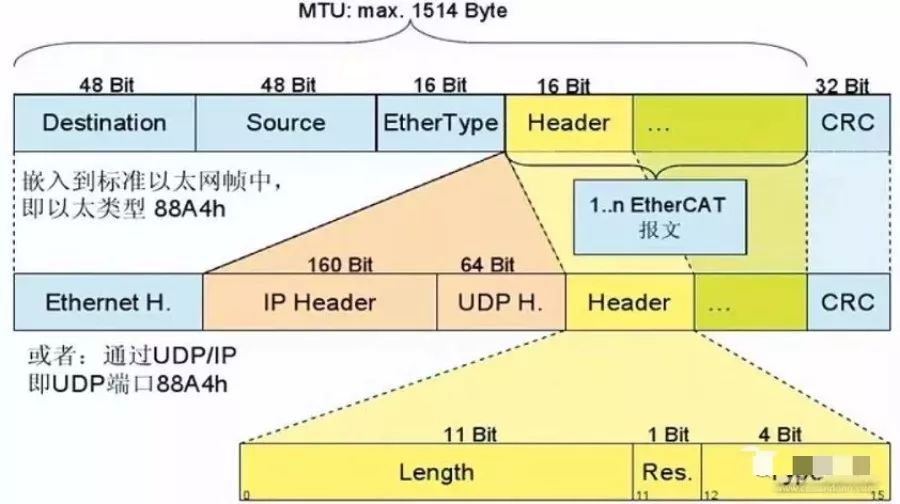

码盘的接口一般都会采用485接口,所以本控制器也采用485的接口,用DMA来实现;伺服控制器与主控制之间的接口有EtherCAT和PROFINET等协议,本控制器采用应用比较广的EtherCAT接口。实时以太网EtherCAT是由倍福开发的一种工业以太网技术。它以高速率、高有效数据利用率、全部符合以太网标准、刷新周期短、同步性能好等优势,在伺服通讯领域中得到慢慢的变多的应用。其原理如图3所示。

主控制器ARM通过STM32F407芯片完成上节介绍的与FPGA的并口通信、EtherCAT通信、485通信。STM32F407属于高端的32位ARM微控制器,该系列芯片是意法半导体(ST)公司出品,其内核是Cortex-M4。本次设计充分的利用其资源,实现了并口通信、therCAT通信、485通信。

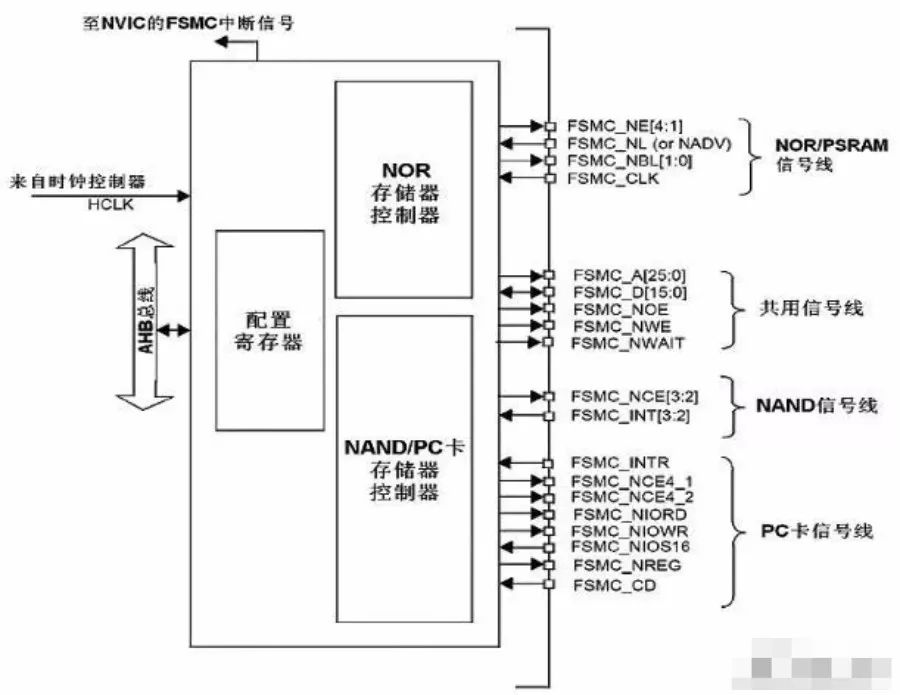

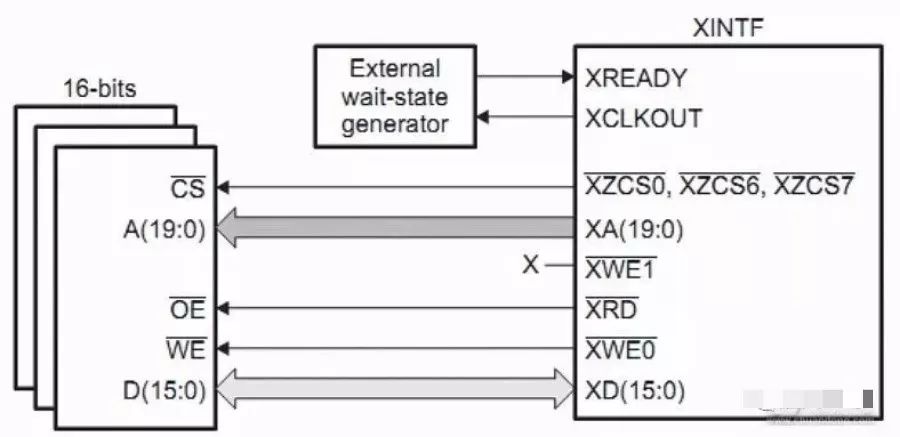

并口通信:STM32F407具有FSMC功能,灵活的静态存储器控制器(FSMC)是内置大容量的外部存储器控制器,使用这个控制器,STM32可以与FPGA或者存储器进行并口通信。FSMC产生所有驱动这些存储器(把FPGA当做存储器来操作)的信号时序:16个数据线个地址线 数据总线XINTF连接框图

EtherCAT通信和485通信:EtherCAT通信通过芯片ET1100来实现,ET1100是一款强大的EtherCAT从站控制器ESC专用芯片,ET1100与ARM的接口采用SPI的方式;485通信速度为2.5Mbps,采用DMA的方式来实现,DMA的具体实现方法在下章软件设计中详述。

FPGA采用Altera的CycloneIV系列FPGA,具有低成本、低功耗的特点,高达532个用户I/O,支持高达200MHz的DDR2SDRAM接口;DSP采用TMS320C28346,通过XINTF连接FPGA,实现双向并口通信。DSP的输入和输出采用中断控制,当FPGA准备好数据后,向DSP发送中断,DSP响应中断后读取相应地址的数据并向另外一段地址写入数据,FPGA等待60μs开始读数据。这样就能完成两个芯片的并行通信。TMS320C28346型DSP芯片有16位XINTF数据总线,做为系统外部接口,它可以与各种外部存储器或者CPU实现无缝连接,如图5所示。在此系统中,将它与FPGA的16个用户可定义I/O管脚相连,用于实现16位并行数据的通信。TMS320C28346芯片可编程通用输入/输出引脚,任选一个和FPGA的用户I/O管脚相连,作为DSP的读写中断。

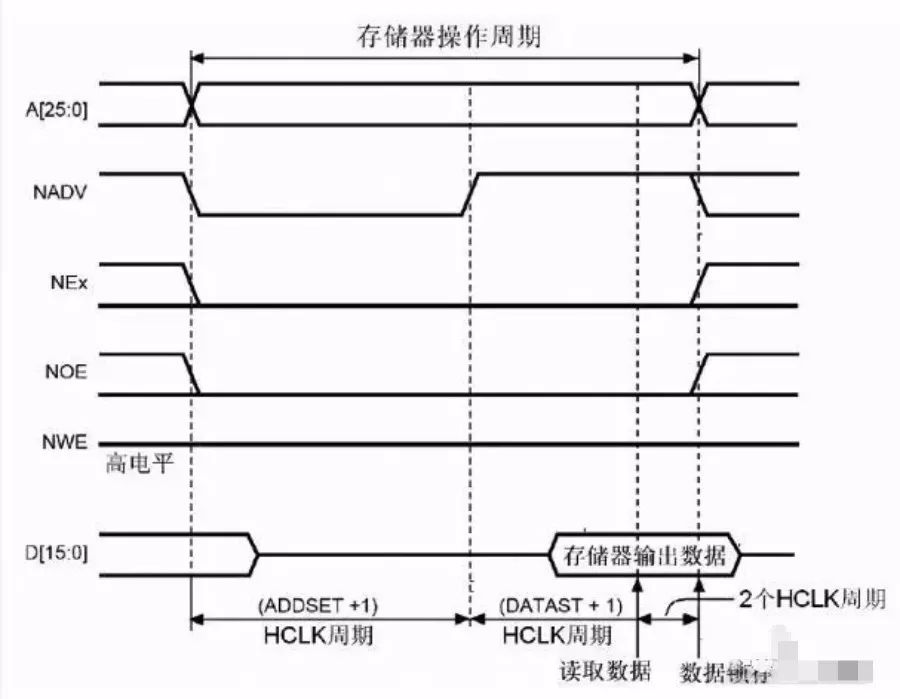

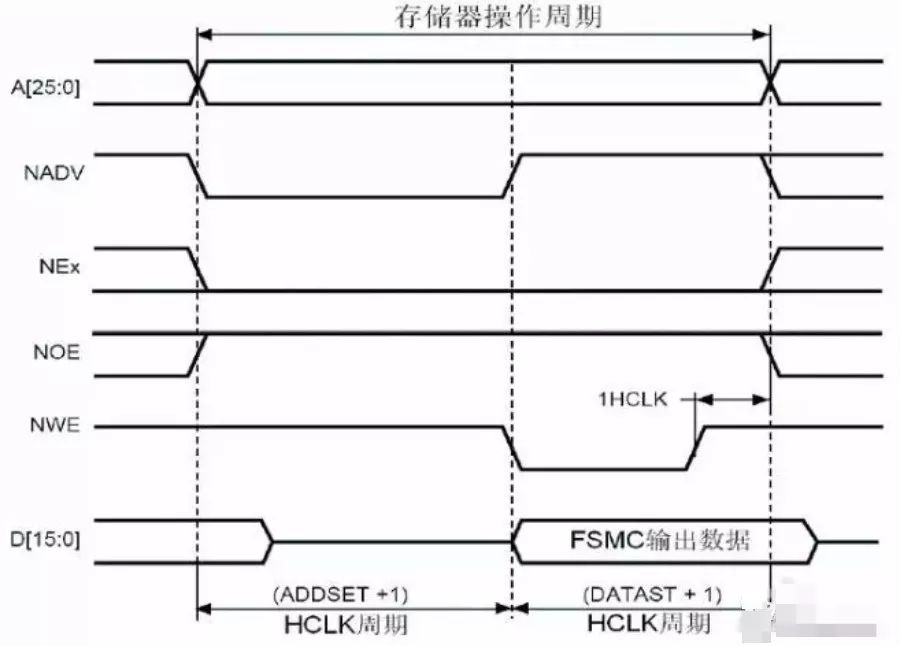

控制器中ARM与FPGA的并口通信用FSMC来实现,采用非总线复用的异步NOR闪存的方式来驱动,读时序如图6所示,写时序如图7所示。

并口通信的地址选择使用了FSMC的BANK1的子板块2,具体程序代码如下:

ARM与FPGA通信触发由外部中断来触发,当FPGA准备好数据后给ARM一个中断,中断周期为120μs,其中前60μs用于ARM从并口地址读取数据并且把要传给FPGA的数据写入相应地址,后60μs用于FPGA从并口地址读取数据,程序代码如下:

ARM与码盘通信通过485来实现,通信速度为2.5Mbps,由于速度快采用一般的中断方式很难满足需求,本系统采用DMA来实现,程序代码如下:

<

FPGA与DSP并行总线通讯模块用于FPGA与DSP之间的并行总线数据交换,其中包含两段独立的地址空间,一个空间用于DSP读FPGA内部数据通道,另一个空间用于DSP向FPGA写数据通道。程序使用ALTERA提供的双口RAM的IP核。程序模块图如图8所示。

FPGA与DSP并行总线通讯模块主时钟CLK的频率应是DSP总线M,这个时钟由FPGA内部的PLL锁相环生成。由于DSP的地址总线位以上,ADDR_DSP连接DSP地址总线的低位。RD_DSP连接DSP读使能,WR_DSP连接DSP写使能,如果有片选信号,DSP读写使能信号需要与片选信号取或后再与WR_DSP和RD_DSP连接。

市面上的伺服驱动器CPU的架构主要有单ARM控制器和单DSP控制器。单ARM控制器方案在通信和控制方面存在一定的优势,但是复杂算法在实现的时候往往会因为运算耗时而降低总系统实时性;单DSP控制器方案中在算法中存下优势,但是在对外通信和控制方面往往会实现起来很复杂。采用ARM+FPGA+DSP架构的多CPU控制器方案完全解决了上述两种方法的弊端,充分的发挥了各个CPU的优势。本文论述的架构在本公司的伺服驱动器产品中做试验和应用,证明了“ARM+FPGA+DSP架构的多CPU控制器架构”的可行性和技术优势。

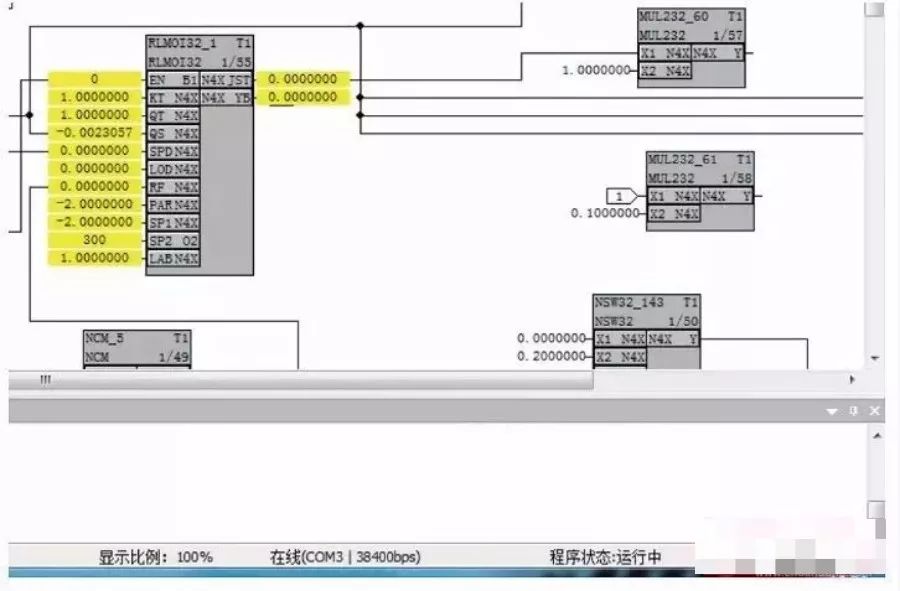

图9 CPU算法在线中的红色标记框图所示,整个伺服驱动器系统的CPU使用率在75.22%(A:空跑时优先级最低的计数器个数;B满算法运行时优先级最低计数器的个数;CPU使用率=(A-B)/A*100),此CPU架构达到了控制CPU使用率和提高系统效率的目标。

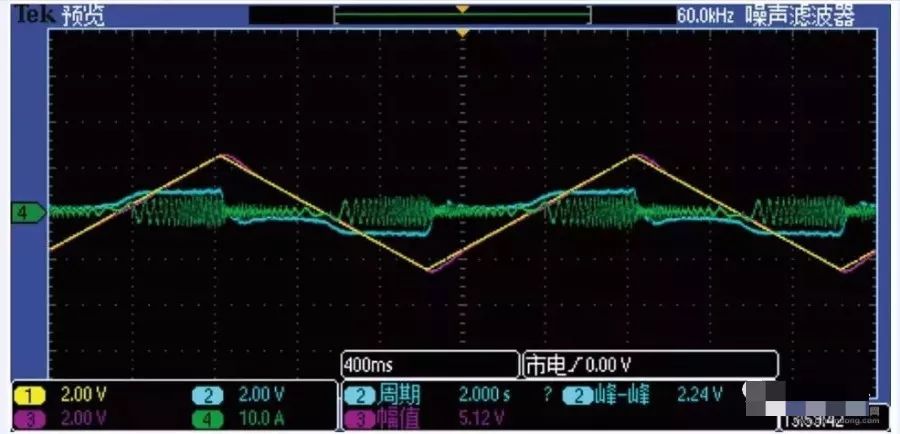

如图10中的离线转速)PI不变时跟随情况,通道1是转速给定,通道2是电磁转矩,通道3是实际转速,通道4是实际A相电流。速度采集首先通过ARM的高速485采集码盘数据,并通过并口传给DSP和FPGA,经过算法处理再把数据下发给码盘,整个闭环过程通过并口传输,满足了伺服驱动器的算法实时性要求,此CPU架构达到了提高总系统实时性的目标。

关键字:编辑:什么鱼 引用地址:论述伺服驱动控制器的实现方法上一篇:变频器谐波的由来、计算及抑制方法下一篇:永磁伺服电机的基本概念及主要传动参数

1 引言 ARINC429 总线具有设计维护方便,与航空电子系统兼容性好等优点,其作为一种重要的.已经广泛的应用于民用飞机上,空客公司的A310 飞机和波音公司的747 飞机均采用了ARINC429 总线。国外对此方向的研究很成熟,Actel 和CONder 等公司均推出了自己的ARINC429 总线产品,其产品大多收发通道在8路以上。国内实现ARINC429 协议大多采用HOLT 公司HS3282 或DEI 公司的DEI1016,采用这类实现方法虽然在某些特定的程度降低了设计难度, 缩短开发周期, 提高了系统可靠性;但在实现多路收发时,不仅成本高, 大幅度提升了PCB 板的面积,而且影响数据的传输速率 。本文将介绍一

本文介绍基于ARM 的来电号码显示器的实现方法。利用CID 芯片HT9032C 来解调FSK 码,同时可实现液晶显示、E2PROM存储和语音播报电话主叫号码等功能,以SPI 串行接口智能显示键盘控制芯片ZLG7289A 为核心设计的键盘电路可实现查阅、删除信息。文章详细的介绍了系统的硬件电路设计和软件流程。实践表明,显示器外围器件少,抗干扰能力强,使用起来更便捷。 目前我国电话网交换机传送主叫识别信息CID(Calling Identity Delivery) 有两种方式,较常用的是FSK(频移键控) 方式,另一种是DTMF(双音多频) 方式。通过掌握相应的协议标准和数据格式,可通过ARM 控制芯片HT9032C 实现解调FSK

随着力矩 传感器 在 工业机器人 领域应用的愈来愈普遍,机器人设备自身不能解决的问题很多。可能你能够找到具体的原因在哪里,最主要的原因有可能是应用程序的问题,有了传感器这样一些问题都会变得简单。 当个人会使用一个机器人手臂,为达到有效载荷、速度和可重复性是最有用的规格参数。其他一些规格参数基本上只是细节,确保所有参数符合您的应用程序。同样的情况出现在FT传感器的规格上。那么怎样选择传感器呢? 接下来主要从5个方面介绍: 一.负荷 当然你必须了解到的主要规格…如果传感器能接受您的应用程序需要的负荷。事实上,如果应用程序需要一个100N载荷在大多数情况下要使用传感器。低频力矩会限制你阅读到一定阈值和一个

1 引言 在80年代中期,为满足不同自动化领域的应用需求,出现了拥有不同技术特点的现场总线。每一种现场总线都有自己的应用领域,并且都力图拓展其应用领域,以扩张其技术垄断范围。但每种现场总线都以一个或几个大型跨国公司为背景,公司的利益与总线的发展息息相关。这一些企业竞争的结果是多种总线协调共存。据不完全统计,目前国际上有200多种现场总线,而其中占据市场主流的现场总线有十几种 。现场总线的多样性,为总线设备用户更好的提供了更多产品选择的同时,也为总线用户带了总线设备间兼容性问题。工厂在扩建,改建等过程中非常有可能会选用与原先现场设备总线标准不同的产品,这些设备由于使用不相同的现场总线,彼此间不能实现数据共享,于是就降低了设备间功能互补

如果在一个系统中拥有几个处理器和外设,要开发具有成本效益、可靠的产品,尤其是在今天很短的产品研究开发时间的条件下,了解所有这些芯片的实时动态特性将变得很重要。实时嵌入式系统慢慢的变多地在多内核ASIC或系统级芯片(SoC)上实现,以利用这一些器件所具有的低功耗、低成本和更高集成度的优点。 开发者所拥有的很多这些标准设计工具是依赖于了解老的技术产品的内部运作情况来实现的,已经不适用于这些新型的、功能强大的多功能设计了。通过集成,SoC架构在单个硅片上拥有多个处理器、存储器、外设、控制器和其它重要的子系统组件。高速内部总线连接这些不同的组件,整体的性能决定于他们之间的数据流的高效管理。瓶颈、延迟和对于像总线和存储器等共享资源的竞争这些

以STM8为例: 将项目使用的MCU型号的icf文件拷贝到项目里面,icf一般放在 C:\Program Files\IAR Systems\Embedded Workbench 6.5\stm8\config 这个目录下. 1、拷贝lnkstm8s207rb.icf 例如,我用的是STM8S207RB,则我会将lnkstm8s207rb.icf这一个文件拷贝到我项目里面。 2、设置项目属性 打开项目的Option属性,然后修改linker-- Linker configuration file这项里面的内容为: $PROJ_DIR$\lnkstm8s207rb.icf 如图, 点确定保存即可。

很多朋友说C中不能精确控制延时时间,不能象汇编那样直观。 其实不然,对延时函数进一步探索一下就能设计出一个理想的框价出来。 一般的我们都用 for(x=100;--x;){;}此句等同与x=100;while(--x){;}; 或for(x=0;x 100;x++){;} 来写一个延时函数。 在这里要格外的注意:X=100,并不表示只运行100个指令时间就跳出循环。 可以了解一下编译后的汇编: x=100;while(--x){;} 汇编后: movlw 100 bcf 3,5 bcf 3,6 movwf_delay l2 decfsz _delay goto l2 return

μC/OS是rosse开发的实时多任务内核,最初是为Motorola 8位处理器68HC11写的。在后来的相关著作中,作者将代码移植到了PC上,以便于更多的读者学习。μC/OSII继承了μC/OS的算法,有执行效率高、占用空间小、实时性强和可扩展性好等特点,被移植到几乎所有类型的CPU上,成为在嵌入式领域非常有一定的影响力的RTOS。然而,由于该实时内核是为8位CPU设计的,对那些具有优先级算法硬件指令的CPU,仅做移植是很不够的。 1 基于优先级的任务调度 一个基于优先级的实时多任务内核的任务调度机制要实现下面三个核心的处理功能: ◆ 将任务置于就绪态; ◆ 将任务取消就绪

解锁【W5500-EVB-Pico】,探秘以太网底层,得捷电子Follow me第4期来袭!

有奖直播 与英飞凌一同革新您的电动汽车温控系统:集成热管理系统(低压侧)

德州仪器新发布符合 AEC-Q100 标准的 MSPM0 MCU,助力优化汽车车身控制模块设计

汽车慢慢的变成了现代人出行的必备工具,随着科学技术的进步,它不仅提供了便捷的交通方式,还慢慢的变成为未来生活的“第三空间”。驾驶者和乘客对汽车 ...

2023年12月21日,中国– 意法半导体发布了STM32 ZeST*(零速满转矩)软件算法。该算法运行在STM32微控制器上,让无感电机驱动器能够在零转 ...

英特尔 Gaudi2C AI 加速卡现身 Linux 驱动,消息称是中国版

12 月 20 日消息,今年 7 月,英特尔面向中国市场推出了一款 Gaudi2 处理器,主要使用在于加速 AI 训练及推理。据 Phoronix 报道 ...

12月19日,摩尔线程首个全国产千卡千亿模型训练平台——摩尔线程KUAE智算中心揭幕仪式在北京成功举办...

现代世界正逐渐采用更自然的人机界面(HMI)。我们不但可以与智能音箱交谈,还可以在纸张般的电子阅读器上阅读。电子科技类产品已是我们的数字 ...

Achronix提供由FPGA赋能的智能网卡(SmartNIC)解决方案来打破智能网络性能极限

开发相关FPGA/DSP总线与接口数据处理消费电子工业电子汽车电子其他技术存储技术综合资讯论坛电子百科词云: